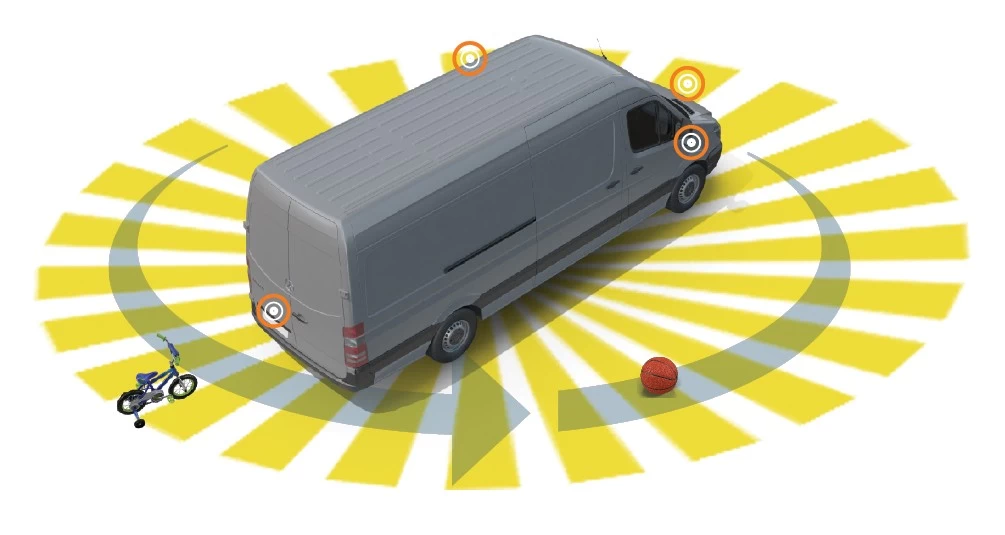

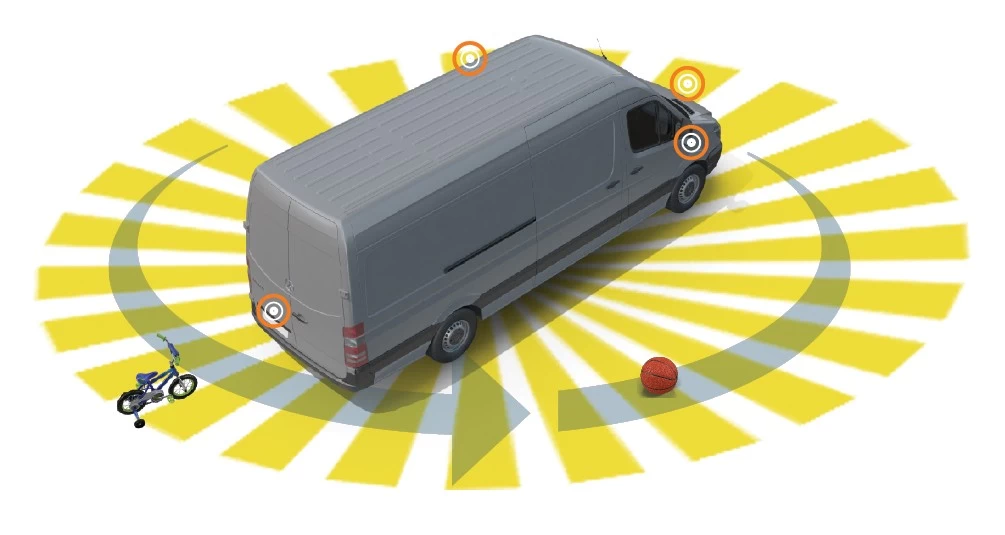

Встроенный дизайн системы Vision Vision 360 °

Richmor

richmor.net

2018-05-16 14:18:01

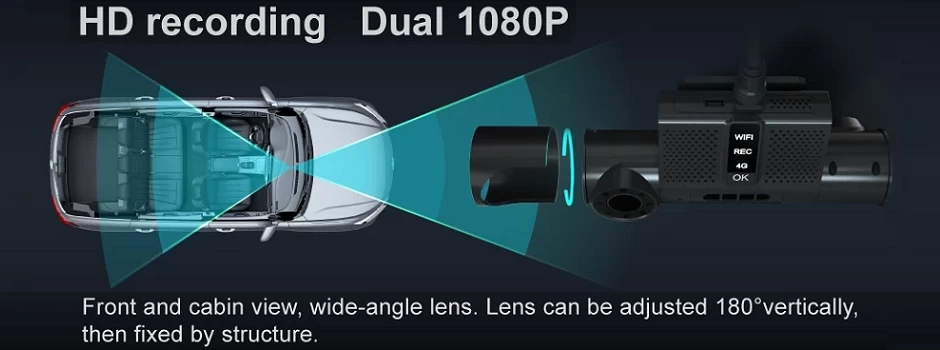

Встроенные 360 ° системы видения с несколькими камерами высокого разрешения вошли в различные приложения, такие как слияние автомобильных датчиков, видеонаблюдение, обнаружение цели и анализ движения. В этом типе системы несколько видеопотоков видео в реальном времени (до 6) объединяются и кадр за кадром обрабатываются для искажений и других корректировок артефактов изображения, корректировки экспозиции и баланса белого, а затем динамически чередуются в панорамную панораму на 360 ° view Он выводится с разрешением 4K и частотой кадров 60 кадров в секунду и, наконец, проецируется на сферическое координатное пространство.

В настоящее время объективы для глазных глаз с высоким разрешением, используемые для таких применений, часто имеют широкоугольное поле зрения (FOV). Одним из самых больших узких мест в системе видеонаблюдения является: входные данные с несколькими камерами хранятся / считываются и получаются из внешней памяти в реальном времени, а затем обрабатываются как один кадр. Аппаратное обеспечение должно завершить операцию обработки между входящими необработанными данными датчика входной камеры и сращиваемым выходным видео в течение одной задержки кадра.

Высокопроизводительные вычислительные платформы продвигались к использованию ПЛИС в сочетании с процессорами для обеспечения специального аппаратного ускорения для задач обработки изображений в реальном времени. Эта конфигурация позволяет процессору сосредоточиться на особенно сложных алгоритмах, где они могут быстро переключать потоки и контексты и назначать повторяющиеся задачи для FPGA, чтобы действовать как настраиваемый аппаратный ускоритель / сопроцессор / механизм разгрузки. Даже если ПЛИС и ЦП используются в качестве дискретных устройств, система может повысить общую эффективность, потому что эти технологии не сталкиваются, но они подходят друг другу, как перчатка на руке.

Например, изображение, полученное из линзы с рыбий глазем, страдает от сильных искажений, и поэтому операция сращивания, созданная на основе нескольких видео камер, является очень сложной вычислительной задачей, поскольку это операция с точечным пикселем. Это сращивание требует много обработки изображений в реальном времени и высокопараллельной архитектуры. Однако это приложение следующего поколения превышает производительность, которую могут продолжать реализовывать ПЛИС, в первую очередь из-за задержки данных пропускной способности чипа. Это, в свою очередь, влияет на общую латентность, пропускную способность и производительность всей системы.

Добавьте интеллектуальную собственность (IP) для полупроводников eFPGA, которая может быть встроена в CPU в SoC. По сравнению с независимым процессором FPGA и процессором, встроенная структура массивов FPGA имеет уникальные преимущества, основное преимущество в том, что производительность более сильная. EFPGA может быть напрямую подключен к ASIC (без буферов ввода-вывода) через широкий параллельный интерфейс, обеспечивая значительно улучшенную пропускную способность и задержку, подсчитываемую в тактовых циклах с одной цифрой. Низкая латентность - это ключ к сложной обработке изображений в реальном времени, например, коррекция искажения объектива с рыбий глаз.

С IP-телефоном Speedcore eFPGA клиенты могут определить свои требования к ресурсам логики, памяти и DSP, а затем Achronix может настроить свой IP-адрес для удовлетворения своих потребностей. Поисковые таблицы (LUT), блоки ячейки памяти и блоки ячейки DSP64 могут быть объединены как блоки для создания наилучшей программируемой структуры для любого конкретного приложения.

В дополнение к модулям стандартной логики, встроенной памяти и модуля DSP клиенты могут определять свои собственные функциональные блоки в структуре eFPGA Speedcore. Интегрируя эти пользовательские функциональные блоки с традиционными строительными блоками в структуру логического массива, можно добавить оптимизированные функции для уменьшения области и повышения производительности целевого приложения, что может значительно повысить производительность eFPGA, особенно для встроенных приложений. Визуальные и алгоритмы обработки изображений очень эффективны

Добавьте интеллектуальную собственность (IP) для полупроводников eFPGA, которая может быть встроена в CPU в SoC. По сравнению с независимым процессором FPGA и процессором, встроенная структура массивов FPGA имеет уникальные преимущества, основное преимущество в том, что производительность более сильная. EFPGA может быть напрямую подключен к ASIC (без буферов ввода-вывода) через широкий параллельный интерфейс, обеспечивая значительно улучшенную пропускную способность и задержку, подсчитываемую в тактовых циклах с одной цифрой. Низкая латентность - это ключ к сложной обработке изображений в реальном времени, например, коррекция искажения объектива с рыбий глаз.

С IP-телефоном Speedcore eFPGA клиенты могут определить свои требования к ресурсам логики, памяти и DSP, а затем Achronix может настроить свой IP-адрес для удовлетворения своих потребностей. Поисковые таблицы (LUT), блоки ячейки памяти и блоки ячейки DSP64 могут быть объединены как блоки для создания наилучшей программируемой структуры для любого конкретного приложения.

В дополнение к модулям стандартной логики, встроенной памяти и модуля DSP клиенты могут определять свои собственные функциональные блоки в структуре eFPGA Speedcore. Интегрируя эти пользовательские функциональные блоки с традиционными строительными блоками в структуру логического массива, можно добавить оптимизированные функции для уменьшения области и повышения производительности целевого приложения, что может значительно повысить производительность eFPGA, особенно для встроенных приложений. Визуальные и алгоритмы обработки изображений очень эффективны

Richmor - это Автомобильные видеомагнитофоны оптовые в Китае. Они предоставили множество видов Автомобильная камера DVR,как Автомобильный видеорегистратор HD с 4-граммовым GPS,

Предыдущий : Эти ужасные методы отслеживания