Embedded 360 ° Vision Vision Design del sistema

Richmor

richmor.net

2018-05-16 14:18:01

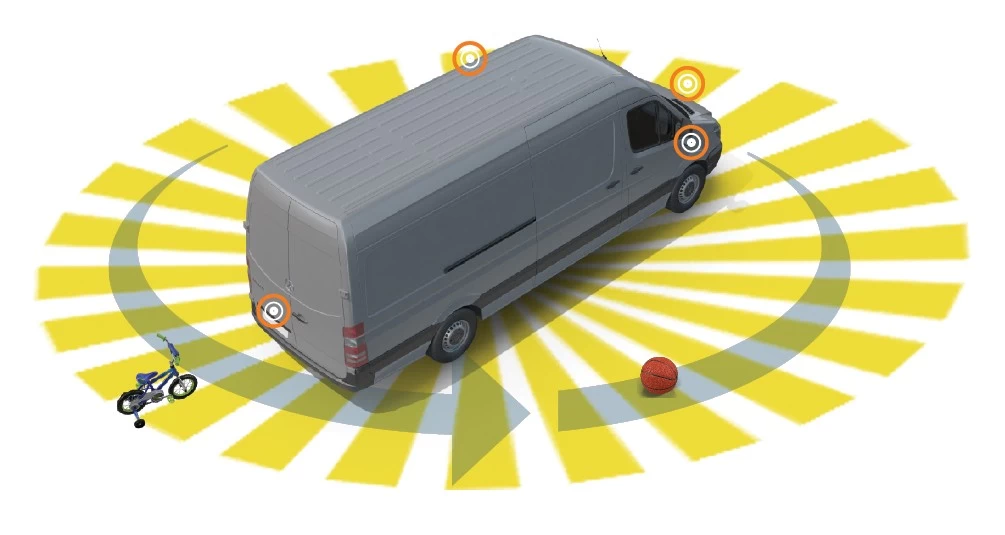

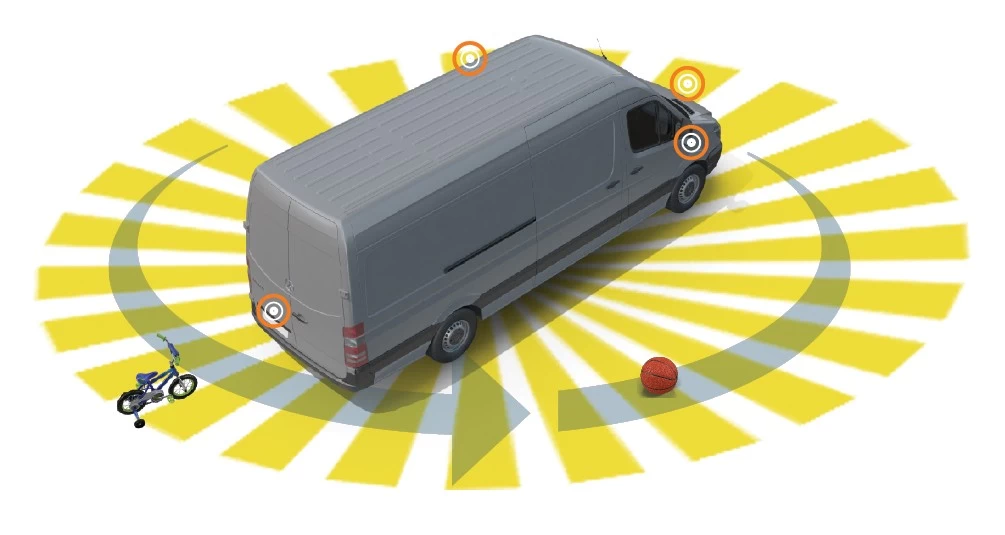

I sistemi di visione a 360 ° incorporati con più telecamere ad alta risoluzione sono entrati in varie applicazioni come la fusione di sensori per autoveicoli, la videosorveglianza, il rilevamento del target e l'analisi del movimento. In questo tipo di sistema, più flussi video della telecamera in tempo reale (fino a 6) vengono aggregati e elaborati fotogramma per fotogramma per la distorsione e altre correzioni di artefatti dell'immagine, regolazioni dell'esposizione e del bilanciamento del bianco e quindi affiancati dinamicamente in una panoramica a 360 ° view Viene emesso a risoluzione 4K e frame rate a 60 fps e infine proiettato su uno spazio di coordinate sferiche.

Le attuali lenti per macchina fotografica ad alta risoluzione con lente fish-eye utilizzate per tali applicazioni hanno spesso un campo visivo grandangolare (FOV). Uno dei maggiori colli di bottiglia nel sistema di telecamere look-a-view è: I dati di ingresso della videocamera multipla sono memorizzati / letti e accessibili dalla memoria esterna in tempo reale e quindi elaborati come un singolo frame. L'hardware deve completare l'operazione di elaborazione tra i dati del sensore raw in entrata della telecamera di input e il video di output giuntato entro un frame delay.

Le piattaforme di elaborazione ad alte prestazioni si stanno muovendo verso l'uso di FPGA in collaborazione con le CPU per fornire un'accelerazione hardware dedicata per le attività di elaborazione delle immagini in tempo reale. Questa configurazione consente alla CPU di concentrarsi su algoritmi particolarmente complessi in cui possono passare rapidamente thread e contesti e assegnare attività ripetitive a un FPGA per fungere da motore di accelerazione / coprocessore / scaricamento hardware configurabile. Anche se l'FPGA e la CPU sono usati come dispositivi discreti, il sistema può migliorare l'efficienza generale perché queste tecnologie non si scontrano, ma si adattano insieme come un guanto sulla mano.

Ad esempio, un'immagine ottenuta da un obiettivo fisheye soffre di una grave distorsione, e quindi un'operazione di splicing generata sulla base di più video della telecamera è un compito altamente intensivo dal punto di vista computazionale, poiché si tratta di un'operazione point-pixel. Questo splicing richiede un sacco di elaborazione delle immagini in tempo reale e un'architettura altamente parallelizzata. Tuttavia, questa applicazione di nuova generazione supera le prestazioni che gli FPGA possono continuare a implementare, principalmente a causa della latenza dei dati di throughput del chip. Ciò a sua volta influisce sulla latenza complessiva del sistema, sulla velocità di trasmissione e sulle prestazioni.

Aggiungi una proprietà intellettuale (IP) dei semiconduttori eFPGA che può essere incorporata con la CPU in un SoC. Rispetto a un chip FPGA indipendente più una soluzione CPU, la struttura dell'array FPGA incorporato ha vantaggi unici, il vantaggio principale è che le prestazioni sono più forti. Un eFPGA può essere collegato direttamente a un ASIC (senza buffer I / O) attraverso un'ampia interfaccia parallela, fornendo un throughput e una latenza significativamente migliorati contati nei cicli di clock a una cifra. La bassa latenza è la chiave per l'elaborazione di immagini complesse in tempo reale, come la correzione della distorsione del fish-eye.

Con Speedcore eFPGA IP, i clienti possono definire i propri requisiti di risorse logiche, di memoria e DSP, e quindi Achronix può configurare il proprio IP in base alle proprie esigenze. Le tabelle di ricerca (LUT), i blocchi di celle RAM e i blocchi di celle DSP64 possono essere combinati come blocchi per creare la migliore struttura programmabile per qualsiasi applicazione specifica.

Oltre ai moduli di logica standard, memoria incorporata e unità DSP, i clienti possono definire i propri blocchi funzione all'interno della struttura eFPGA di Speedcore. Integrando questi blocchi funzione personalizzati con i blocchi di costruzione tradizionali nella struttura dell'array logico, è possibile aggiungere funzioni ottimizzate per ridurre l'area e migliorare le prestazioni dell'applicazione di destinazione, che può migliorare notevolmente le prestazioni dell'eFPGA, in particolare per le applicazioni incorporate. Gli algoritmi di elaborazione visiva e di immagine sono molto efficaci

Aggiungi una proprietà intellettuale (IP) dei semiconduttori eFPGA che può essere incorporata con la CPU in un SoC. Rispetto a un chip FPGA indipendente più una soluzione CPU, la struttura dell'array FPGA incorporato ha vantaggi unici, il vantaggio principale è che le prestazioni sono più forti. Un eFPGA può essere collegato direttamente a un ASIC (senza buffer I / O) attraverso un'ampia interfaccia parallela, fornendo un throughput e una latenza significativamente migliorati contati nei cicli di clock a una cifra. La bassa latenza è la chiave per l'elaborazione di immagini complesse in tempo reale, come la correzione della distorsione del fish-eye.

Con Speedcore eFPGA IP, i clienti possono definire i propri requisiti di risorse logiche, di memoria e DSP, e quindi Achronix può configurare il proprio IP in base alle proprie esigenze. Le tabelle di ricerca (LUT), i blocchi di celle RAM e i blocchi di celle DSP64 possono essere combinati come blocchi per creare la migliore struttura programmabile per qualsiasi applicazione specifica.

Oltre ai moduli di logica standard, memoria incorporata e unità DSP, i clienti possono definire i propri blocchi funzione all'interno della struttura eFPGA di Speedcore. Integrando questi blocchi funzione personalizzati con i blocchi di costruzione tradizionali nella struttura dell'array logico, è possibile aggiungere funzioni ottimizzate per ridurre l'area e migliorare le prestazioni dell'applicazione di destinazione, che può migliorare notevolmente le prestazioni dell'eFPGA, in particolare per le applicazioni incorporate. Gli algoritmi di elaborazione visiva e di immagine sono molto efficaci

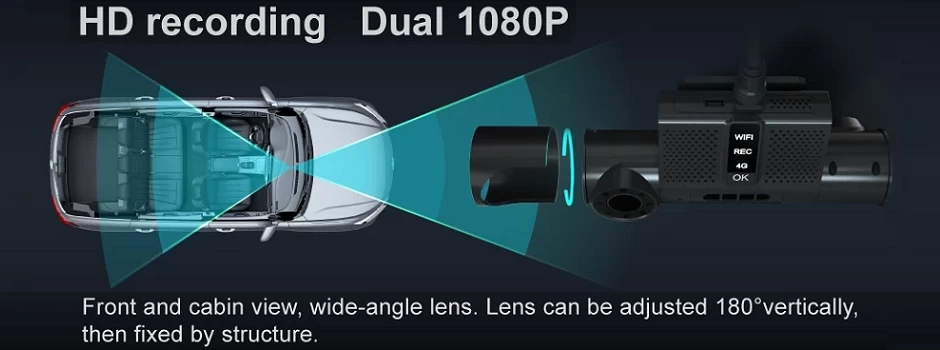

Richmor è un Commercianti di videoregistratori per veicoli in Cina. Hanno fornito molti tipi di sistema di telecamere per auto DVR HD,piace DVR veicolo HD con GPS 4g.

Precedente : Quelle terribili tecniche di localizzazione