Design de Sistema de Visão Vision 360 ° Embutido

Richmor

richmor.net

2018-05-16 14:18:01

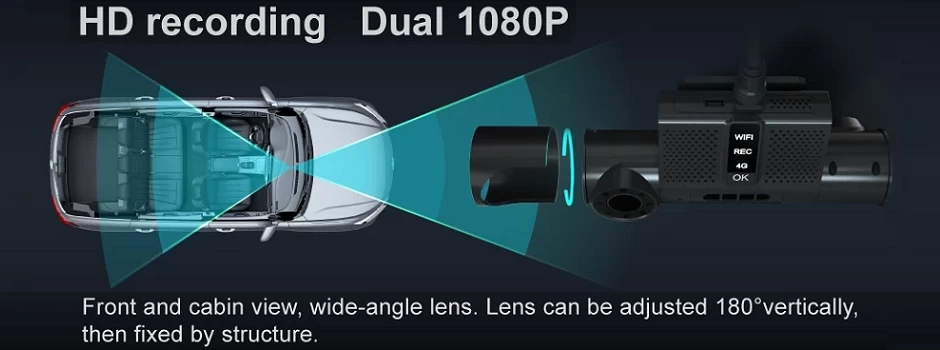

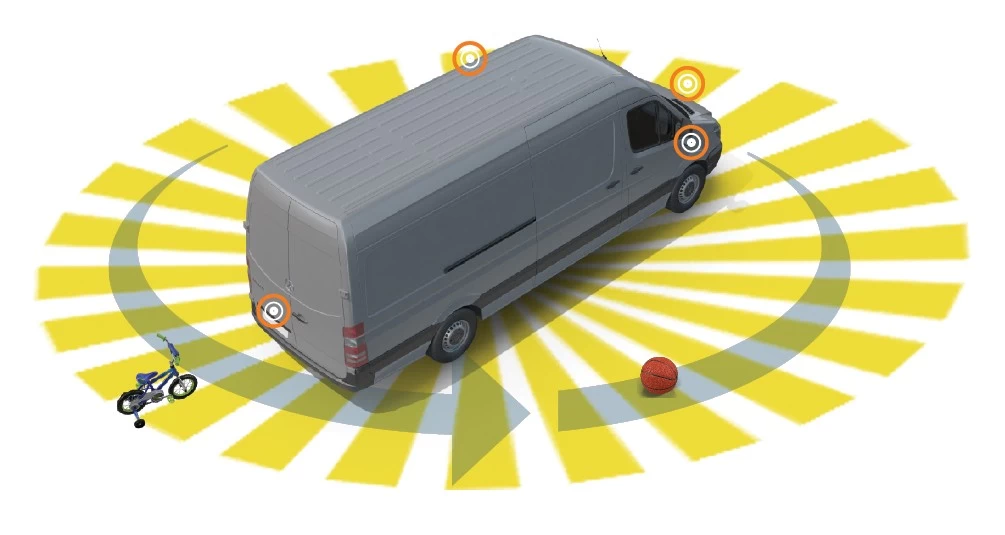

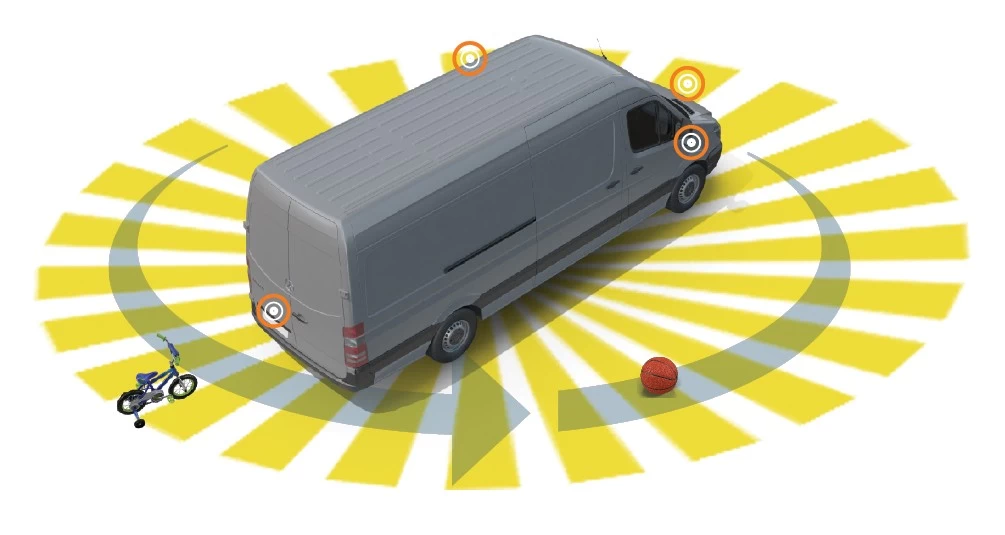

Os sistemas integrados de visão de visão 360 ° com múltiplas câmeras de alta resolução entraram em várias aplicações, como fusão de sensores automotivos, vigilância por vídeo, detecção de alvos e análise de movimento. Nesse tipo de sistema, vários fluxos de vídeo de câmera em tempo real (até 6) são agregados e quadro a quadro processados para distorção e outras correções de artefatos de imagem, ajustes de exposição e balanço de branco e, em seguida, dinamicamente lado a lado em 360 ° panorâmico É emitido em resolução 4K e taxa de quadros de 60 fps e finalmente projetado em um espaço de coordenadas esféricas.

As lentes atuais de câmera de olho de peixe de alta resolução usadas para tais aplicações geralmente têm um campo de visão de ângulo amplo (FOV). Um dos maiores gargalos no sistema de câmeras de visualização é: Os dados de entrada de várias câmeras são armazenados / lidos e acessados da memória externa em tempo real e processados como um único quadro. O hardware precisa concluir a operação de processamento entre os dados do sensor bruto de entrada da câmera de entrada e o vídeo de saída processado dentro de um atraso de quadro.

As plataformas de computação de alto desempenho estão se movendo em direção ao uso de FPGAs em conjunto com CPUs para fornecer aceleração de hardware dedicada para tarefas de processamento de imagem em tempo real. Essa configuração permite que a CPU se concentre em algoritmos particularmente complexos, nos quais pode alternar rapidamente encadeamentos e contextos e atribuir tarefas repetitivas a um FPGA para atuar como um acelerador / coprocessador / mecanismo de descarregamento de hardware configurável. Mesmo que o FPGA e a CPU sejam usados como dispositivos discretos, o sistema pode melhorar a eficiência geral porque essas tecnologias não colidem, mas elas se encaixam como uma luva na mão.

Por exemplo, uma imagem obtida de uma lente olho de peixe sofre de distorção severa e, portanto, uma operação de emenda gerada com base em vários vídeos de câmera é uma tarefa altamente computacionalmente intensiva porque é uma operação de ponto-pixel. Essa emenda requer muito processamento de imagem em tempo real e uma arquitetura altamente paralelizada. No entanto, este aplicativo de próxima geração excede o desempenho que os FPGAs podem continuar implementando, principalmente devido à latência dos dados de taxa de transferência do chip. Isso, por sua vez, afeta a latência geral, a taxa de transferência e o desempenho geral do sistema.

Adicione uma propriedade intelectual (IP) de semicondutor eFPGA que possa ser incorporada à CPU em um SoC. Em comparação com um chip FPGA independente e uma solução de CPU, a estrutura de matriz FPGA incorporada tem vantagens exclusivas, a principal vantagem é que o desempenho é mais forte. Um eFPGA pode ser conectado diretamente a um ASIC (sem buffers de E / S) por meio de uma ampla interface paralela, fornecendo throughput e latência significativamente melhorados, contados em ciclos de clock de um dígito. A baixa latência é a chave para o processamento complexo de imagens em tempo real, como a correção da distorção da lente olho de peixe.

Com o Speedface eFPGA IP, os clientes podem definir seus requisitos de lógica, memória e recursos de DSP e, em seguida, o Achronix pode configurar seu IP para atender às suas necessidades. As tabelas de consulta (LUTs), os blocos de células RAM e os blocos de células DSP64 podem ser combinados como blocos para criar a melhor estrutura programável para qualquer aplicação.

Além dos módulos de lógica padrão, memória embarcada e unidade DSP, os clientes podem definir seus próprios blocos de função dentro da estrutura do SpeedScore eFPGA. Ao integrar esses blocos de funções personalizadas aos blocos de construção tradicionais na estrutura do array lógico, funções otimizadas podem ser adicionadas para reduzir a área e melhorar o desempenho do aplicativo de destino, o que pode melhorar muito o desempenho do eFPGA, especialmente para aplicativos incorporados. Algoritmos de processamento visual e de imagem são muito eficazes

Adicione uma propriedade intelectual (IP) de semicondutor eFPGA que possa ser incorporada à CPU em um SoC. Em comparação com um chip FPGA independente e uma solução de CPU, a estrutura de matriz FPGA incorporada tem vantagens exclusivas, a principal vantagem é que o desempenho é mais forte. Um eFPGA pode ser conectado diretamente a um ASIC (sem buffers de E / S) por meio de uma ampla interface paralela, fornecendo throughput e latência significativamente melhorados, contados em ciclos de clock de um dígito. A baixa latência é a chave para o processamento complexo de imagens em tempo real, como a correção da distorção da lente olho de peixe.

Com o Speedface eFPGA IP, os clientes podem definir seus requisitos de lógica, memória e recursos de DSP e, em seguida, o Achronix pode configurar seu IP para atender às suas necessidades. As tabelas de consulta (LUTs), os blocos de células RAM e os blocos de células DSP64 podem ser combinados como blocos para criar a melhor estrutura programável para qualquer aplicação.

Além dos módulos de lógica padrão, memória embarcada e unidade DSP, os clientes podem definir seus próprios blocos de função dentro da estrutura do SpeedScore eFPGA. Ao integrar esses blocos de funções personalizadas aos blocos de construção tradicionais na estrutura do array lógico, funções otimizadas podem ser adicionadas para reduzir a área e melhorar o desempenho do aplicativo de destino, o que pode melhorar muito o desempenho do eFPGA, especialmente para aplicativos incorporados. Algoritmos de processamento visual e de imagem são muito eficazes

Richmor é um Gravador de vídeo do veículo por atacado na China. Eles forneceram muitos tipos de sistema da câmera do carro DVR do hd,gostar Veículo HD DVR com GPS 4g.