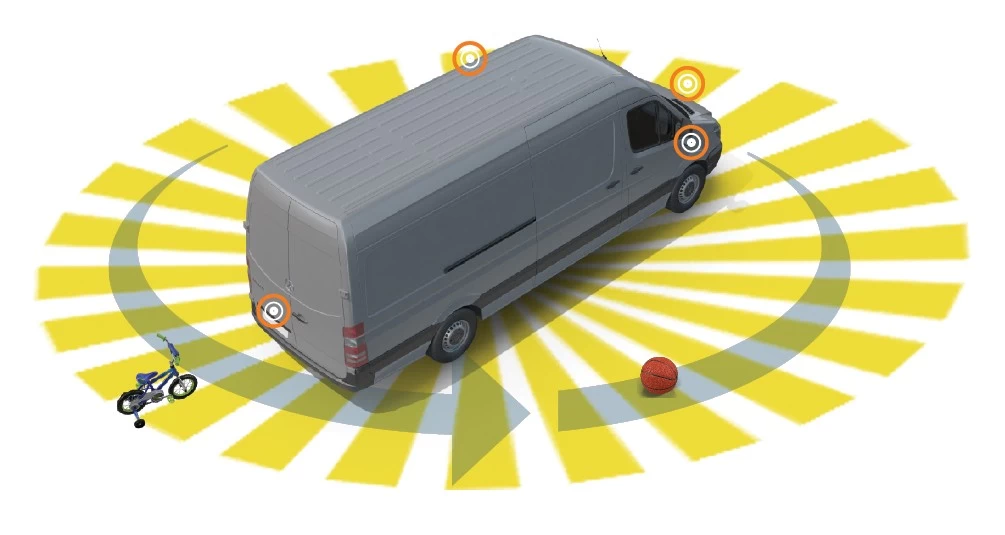

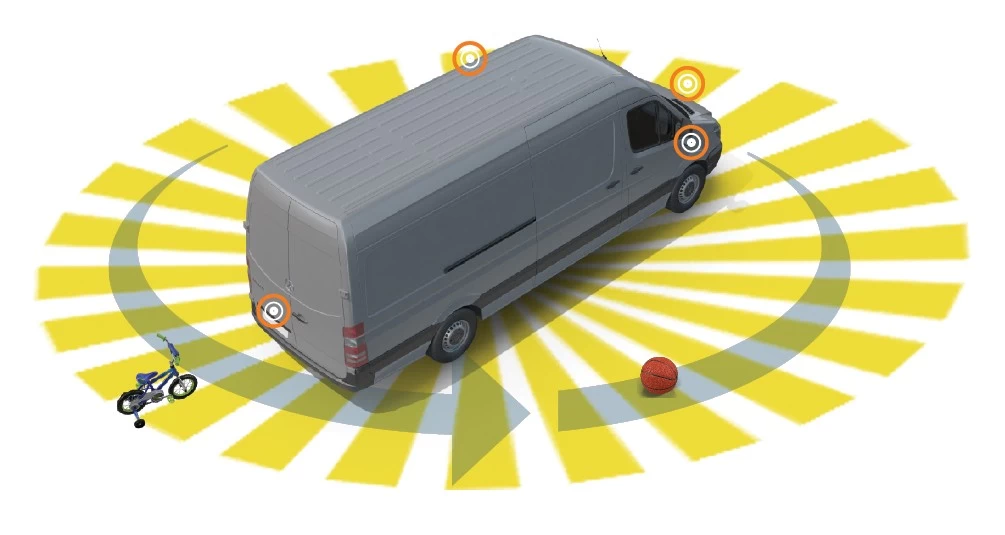

Conception de système Vision Vision intégrée à 360 °

richmor

richmor.net

2018-05-16 14:18:01

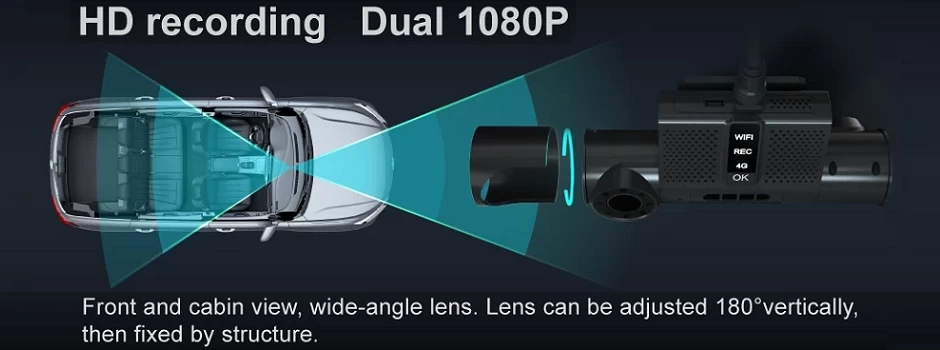

Des systèmes de vision intégrés à 360 ° avec plusieurs caméras à haute résolution ont pénétré dans diverses applications telles que la fusion de capteurs automobiles, la vidéosurveillance, la détection de cibles et l'analyse de mouvement. Dans ce type de système, plusieurs flux vidéo de caméra en temps réel (jusqu'à 6) sont agrégés et traités image par image pour la distorsion et autres corrections d'image, l'exposition et les ajustements de balance des blancs, puis dynamiquement transformés en panoramique 360 °. view Il est sorti à une résolution de 4K et à une vitesse de trame de 60 fps et finalement projeté sur un espace de coordonnées sphérique.

Les lentilles actuelles à haute résolution pour les yeux de poisson utilisées pour de telles applications ont souvent un champ de vision grand angle (FOV). L'un des plus gros goulets d'étranglement dans le système de caméra de visualisation est: Les données d'entrée multi-caméras sont stockées / lues et accessibles depuis la mémoire externe en temps réel, puis traitées comme une seule image. Le matériel doit terminer l'opération de traitement entre les données de capteur brutes entrantes de la caméra d'entrée et la vidéo de sortie épissée dans un délai d'une trame.

Les plates-formes informatiques haute performance se sont tournées vers l'utilisation de FPGA en conjonction avec des processeurs pour fournir une accélération matérielle dédiée pour les tâches de traitement d'image en temps réel. Cette configuration permet au CPU de se concentrer sur des algorithmes particulièrement complexes, où ils peuvent rapidement changer de threads et de contextes et assigner des tâches répétitives à un FPGA pour agir comme un accélérateur / coprocesseur / moteur de déchargement matériel configurable. Même si le FPGA et le CPU sont utilisés comme des dispositifs discrets, le système peut améliorer l'efficacité globale parce que ces technologies ne se heurtent pas, mais elles s'emboîtent comme un gant sur la main.

Par exemple, une image obtenue à partir d'un objectif fisheye souffre d'une distorsion sévère, et ainsi une opération d'épissage générée sur la base de plusieurs vidéos d'appareil photo est une tâche hautement computationnelle car il s'agit d'une opération de pixel ponctuel. Cette épissure nécessite beaucoup de traitement d'image en temps réel et une architecture fortement parallélisée. Cependant, cette application de nouvelle génération dépasse les performances que les FPGA peuvent continuer à mettre en œuvre, principalement en raison de la latence des données de débit de la puce. Cela affecte à son tour la latence globale du système, la vitesse de traitement et les performances.

Ajouter une propriété intellectuelle (IP) semi-conducteur eFPGA pouvant être intégrée à la CPU dans un SoC. Comparée à une solution FPGA plus puce CPU indépendante, la structure de la baie FPGA embarquée présente des avantages uniques, le principal avantage étant que les performances sont plus élevées. Un eFPGA peut être directement connecté à un ASIC (sans tampons d'E / S) via une large interface parallèle, ce qui améliore considérablement le débit et la latence des cycles d'horloge à un chiffre. La faible latence est la clé du traitement en temps réel de l'image complexe, comme la correction de la distorsion de l'objectif fisheye.

Avec Speedcore eFPGA IP, les clients peuvent définir leurs besoins en termes de logique, de mémoire et de DSP, puis Achronix peut configurer leur IP pour répondre à leurs besoins. Les tables de consultation (LUT), les blocs de cellules RAM et les blocs de cellules DSP64 peuvent être combinés comme des blocs pour créer la meilleure structure programmable pour une application donnée.

En plus de la logique standard, de la mémoire intégrée et des modules d'unités DSP, les clients peuvent définir leurs propres blocs fonctionnels dans la structure Speedcore eFPGA. En intégrant ces blocs fonctionnels personnalisés aux blocs de construction traditionnels dans la structure logique, des fonctions optimisées peuvent être ajoutées pour réduire la surface et améliorer les performances de l'application cible, ce qui peut grandement améliorer les performances de l'eFPGA, notamment pour les applications embarquées. Les algorithmes de traitement visuel et d'image sont très efficaces

Ajouter une propriété intellectuelle (IP) semi-conducteur eFPGA pouvant être intégrée à la CPU dans un SoC. Comparée à une solution FPGA plus puce CPU indépendante, la structure de la baie FPGA embarquée présente des avantages uniques, le principal avantage étant que les performances sont plus élevées. Un eFPGA peut être directement connecté à un ASIC (sans tampons d'E / S) via une large interface parallèle, ce qui améliore considérablement le débit et la latence des cycles d'horloge à un chiffre. La faible latence est la clé du traitement en temps réel de l'image complexe, comme la correction de la distorsion de l'objectif fisheye.

Avec Speedcore eFPGA IP, les clients peuvent définir leurs besoins en termes de logique, de mémoire et de DSP, puis Achronix peut configurer leur IP pour répondre à leurs besoins. Les tables de consultation (LUT), les blocs de cellules RAM et les blocs de cellules DSP64 peuvent être combinés comme des blocs pour créer la meilleure structure programmable pour une application donnée.

En plus de la logique standard, de la mémoire intégrée et des modules d'unités DSP, les clients peuvent définir leurs propres blocs fonctionnels dans la structure Speedcore eFPGA. En intégrant ces blocs fonctionnels personnalisés aux blocs de construction traditionnels dans la structure logique, des fonctions optimisées peuvent être ajoutées pour réduire la surface et améliorer les performances de l'application cible, ce qui peut grandement améliorer les performances de l'eFPGA, notamment pour les applications embarquées. Les algorithmes de traitement visuel et d'image sont très efficaces

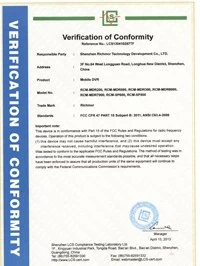

Richmor est un Enregistreur vidéo de véhicule en gros en Chine.Ils ont fourni de nombreux types de système de caméra DVR hd voiture,comme DVR de véhicule HD avec GPS 4g.