Embedded 360 ° Vision Vision System Design

richmor

richmor.net

2018-05-16 14:18:01

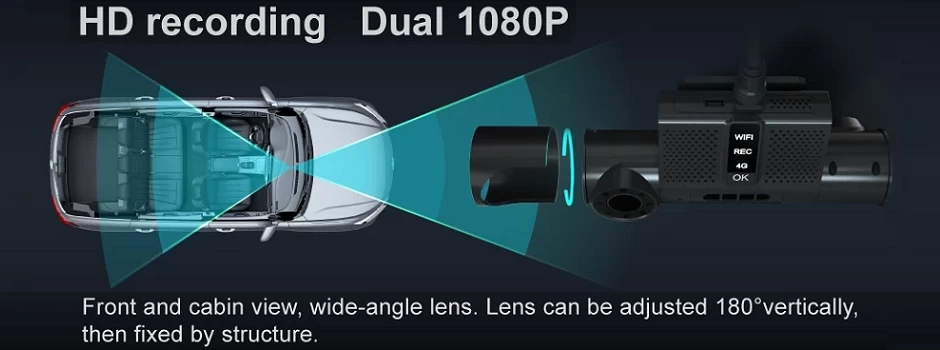

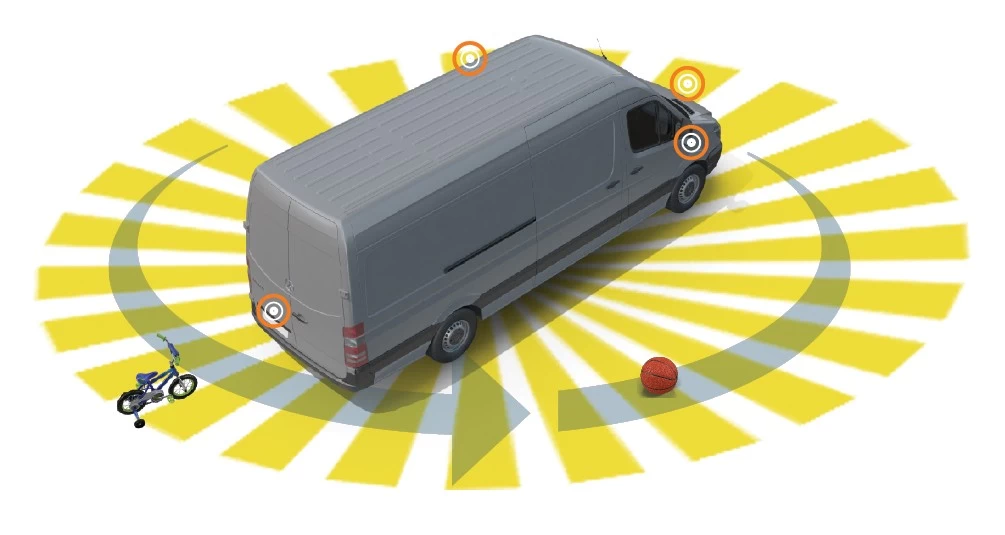

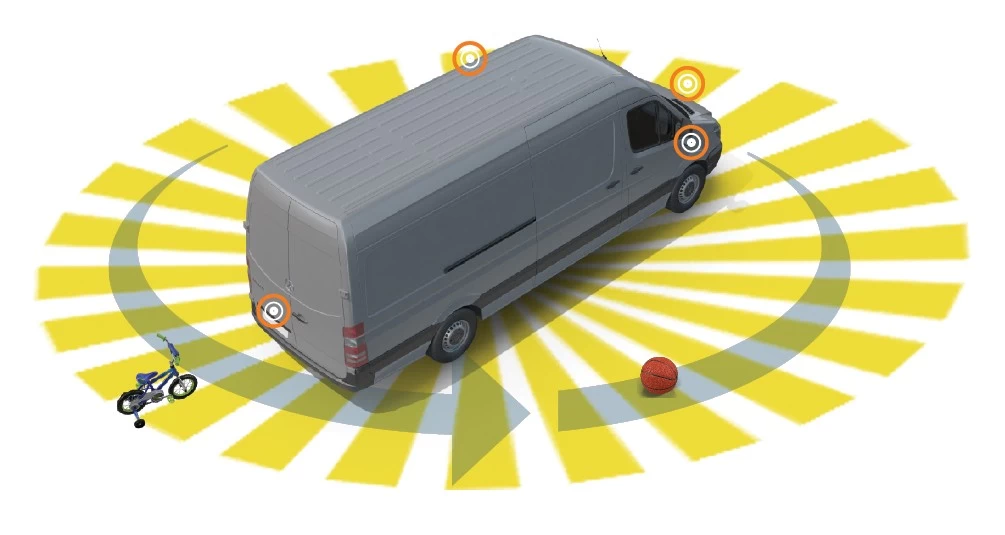

Los sistemas integrados de visión de 360 ° con múltiples cámaras de alta resolución han ingresado a diversas aplicaciones, como fusión de sensores automotrices, videovigilancia, detección de objetivos y análisis de movimiento. En este tipo de sistema, varias secuencias de video de cámara en tiempo real (hasta 6) se agregan y procesan cuadro por cuadro para la corrección de distorsiones y otras imágenes, ajustes de exposición y balance de blancos, y luego se colocan dinámicamente en una panorámica de 360 ° view Se emite a una resolución de 4K y a una velocidad de cuadro de 60 fps y finalmente se proyecta en un espacio de coordenadas esféricas.

Las lentes de cámara de ojo de pez de alta resolución actuales utilizadas para tales aplicaciones a menudo tienen un campo de visión gran angular (FOV). Uno de los principales cuellos de botella en el sistema de cámara de mirada-a-vista es: Los datos de entrada de varias cámaras se almacenan / leen y se accede desde la memoria externa en tiempo real, y luego se procesan como un solo cuadro. El hardware debe completar la operación de procesamiento entre los datos del sensor sin formato entrante de la cámara de entrada y el video de salida empalmado dentro de un retraso de cuadro.

Las plataformas informáticas de alto rendimiento se han estado moviendo hacia el uso de FPGA junto con CPU para proporcionar aceleración de hardware dedicada para tareas de procesamiento de imágenes en tiempo real. Esta configuración permite a la CPU centrarse en algoritmos particularmente complejos donde pueden cambiar rápidamente los hilos y contextos y asignar tareas repetitivas a un FPGA para actuar como un acelerador de hardware configurable / motor de coprocesador / descarga. Incluso si el FPGA y la CPU se usan como dispositivos discretos, el sistema puede mejorar la eficiencia general porque estas tecnologías no colisionan, pero se ajustan juntas como un guante en la mano.

Por ejemplo, una imagen obtenida de una lente de ojo de pez sufre una distorsión severa y, por lo tanto, una operación de empalme generada en base a múltiples videos de la cámara es una tarea altamente computacionalmente intensiva debido a que es una operación punto-píxel. Este empalme requiere mucho procesamiento de imágenes en tiempo real y una arquitectura altamente paralelizada. Sin embargo, esta aplicación de próxima generación excede el rendimiento que los FPGA pueden continuar implementando, principalmente debido a la latencia de los datos de rendimiento del chip. Esto, a su vez, afecta la latencia general, la velocidad de rendimiento y el rendimiento del sistema en general.

Agregue una propiedad intelectual (IP) de semiconductor eFPGA que pueda integrarse con la CPU en un SoC. En comparación con una solución independiente de CPU y chip FPGA, la estructura de matriz FPGA incorporada tiene ventajas únicas, la principal ventaja es que el rendimiento es más fuerte. Un eFPGA se puede conectar directamente a un ASIC (sin búferes de E / S) a través de una amplia interfaz paralela, proporcionando un rendimiento significativamente mejorado y latencia contada en ciclos de reloj de un solo dígito. La baja latencia es la clave para el procesamiento complejo de imágenes en tiempo real, como la corrección de la distorsión de la lente ojo de pez.

Con Speedcore eFPGA IP, los clientes pueden definir sus requisitos de recursos de lógica, memoria y DSP, y luego Achronix puede configurar su IP para satisfacer sus necesidades. Las tablas de búsqueda (LUT), los bloques de celdas RAM y los bloques de celdas DSP64 se pueden combinar como bloques para crear la mejor estructura programable para cualquier aplicación determinada.

Además de la lógica estándar, la memoria incorporada y los módulos de unidades DSP, los clientes pueden definir sus propios bloques de funciones dentro de la estructura de Speedcore eFPGA. Al integrar estos bloques de funciones personalizadas con los bloques de construcción tradicionales en la estructura de matriz lógica, se pueden agregar funciones optimizadas para reducir el área y mejorar el rendimiento de la aplicación de destino, lo que puede mejorar enormemente el rendimiento de eFPGA, especialmente para aplicaciones integradas. Los algoritmos de procesamiento visual e imagen son muy efectivos

Agregue una propiedad intelectual (IP) de semiconductor eFPGA que pueda integrarse con la CPU en un SoC. En comparación con una solución independiente de CPU y chip FPGA, la estructura de matriz FPGA incorporada tiene ventajas únicas, la principal ventaja es que el rendimiento es más fuerte. Un eFPGA se puede conectar directamente a un ASIC (sin búferes de E / S) a través de una amplia interfaz paralela, proporcionando un rendimiento significativamente mejorado y latencia contada en ciclos de reloj de un solo dígito. La baja latencia es la clave para el procesamiento complejo de imágenes en tiempo real, como la corrección de la distorsión de la lente ojo de pez.

Con Speedcore eFPGA IP, los clientes pueden definir sus requisitos de recursos de lógica, memoria y DSP, y luego Achronix puede configurar su IP para satisfacer sus necesidades. Las tablas de búsqueda (LUT), los bloques de celdas RAM y los bloques de celdas DSP64 se pueden combinar como bloques para crear la mejor estructura programable para cualquier aplicación determinada.

Además de la lógica estándar, la memoria incorporada y los módulos de unidades DSP, los clientes pueden definir sus propios bloques de funciones dentro de la estructura de Speedcore eFPGA. Al integrar estos bloques de funciones personalizadas con los bloques de construcción tradicionales en la estructura de matriz lógica, se pueden agregar funciones optimizadas para reducir el área y mejorar el rendimiento de la aplicación de destino, lo que puede mejorar enormemente el rendimiento de eFPGA, especialmente para aplicaciones integradas. Los algoritmos de procesamiento visual e imagen son muy efectivos

Richmor es un Videograbador de vehículo por mayor en China. Han proporcionado muchos tipos de Sistema de cámara DVR para coche HD,me gusta HD vehículo DVR con 4g GPS.